Hi,

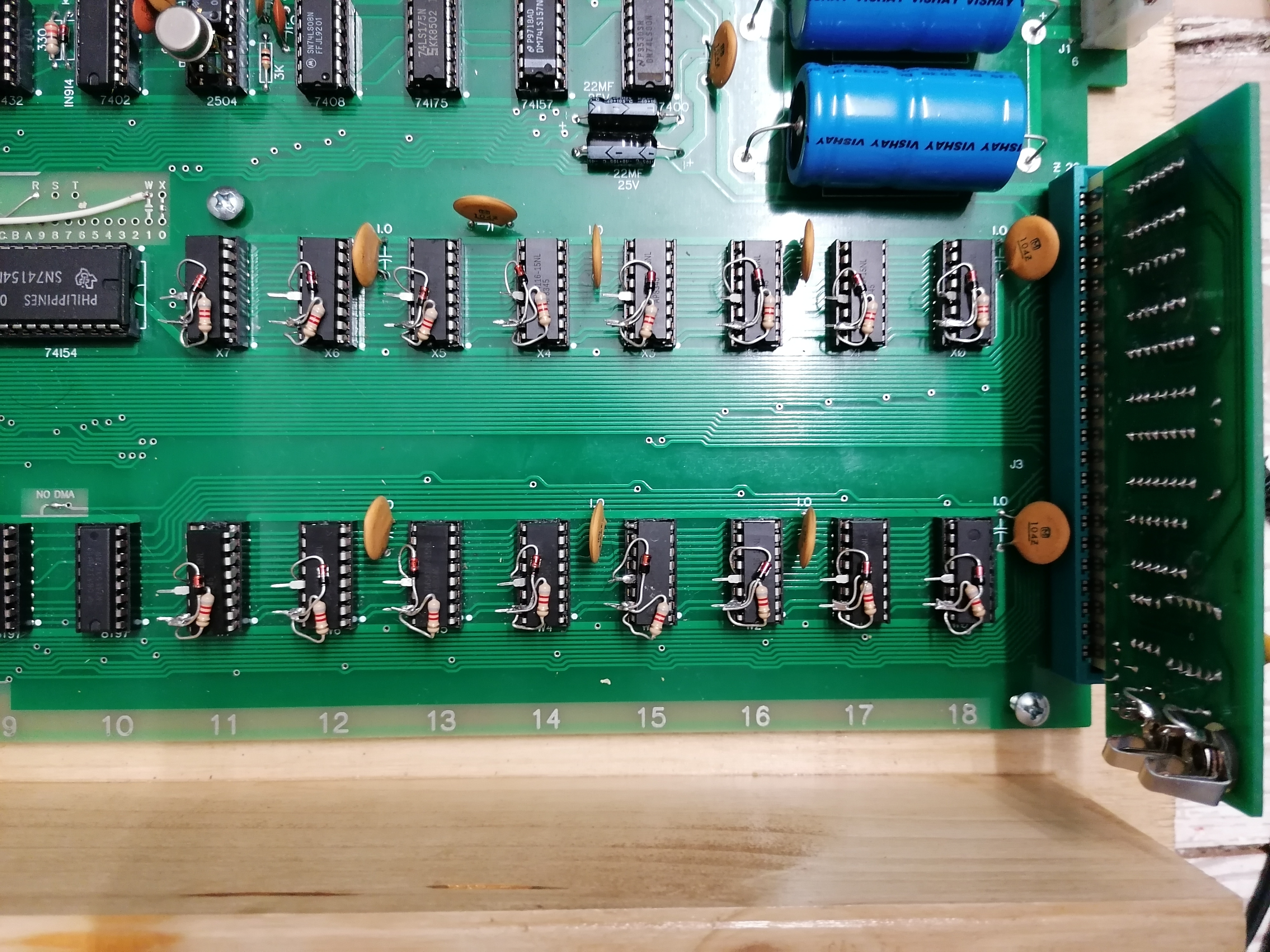

I would like to share with you the solution I used on my board to replace the expansive MK4096 dram with the more economic 4116. Keep in mind that this ram will behave exactly as the MK4096, so only 4k per bank will be aviable.ERRATA CORRIGE: dram pin 13 must be connected to GND and not left unconnected.This solution was tested and works perfectly on my board since September 1st 2022.

Well done

I wonder with SMT devices it could all be hidden on the underside of the chip too.

I also did put 4116 into one of my Apple-1 to get 20 kByte of RAM.

It almost worked. "Almost" meaning that only longer runs of a good RAM test program could unveil that it didn't work perfectly.

This problem has been traced to a severe difference in the 16k bit generation DRAMs to the prior ones: the prior ones (4096 and 4027) keep their output data driven until the next access cycle, while the 16k bit generation turns the output drivers off (to tristate) when /CAS is deasserted.

And from this point on, the data within the isolated data bus of the DRAM subsystem starts to crumble. What the 6502 then reads is bit "vapor" - to use a very precise term coined by Don Lancaster for his "vapor lock" technique.

Reading bit vapors as the wanted data may or may not work. It depends on the timing of the individual Apple-1. I had to add 39 pF capacitors to the Douts of the 4116 to make it work better. It's still not perfect. DRAM test from my diagnostics still find a DRAM fault every few minutes or so.

The real remedy is to generate new DRAM timing tailored to said vices of the 4116 (o later) DRAM generation(s). I wrote about this in my DRAM card thread here on Applefritter.

The irony is that this feature found until 2nd generation DRAMs (4k bit) and was "stolen" from the 16k bit DRAM generation upwards later came back as "EDO", or "Extended Data Out".

- Uncle Bernie

There is a period of data bus float on the Apple 1 but the 4K DRAM is no better than the 16K DRAM because the 8T97’s tri-state the RAM data a little before the end of CAS. The data bus is very capacitive, I estimate about 100 pf. I added 3.3K pull-up resistors to the data lines and could still run the memory test for a day without failure. My measurements were that the float time that mattered was about 30 nsec for my system, but that could potentially vary with different 6502’s. The system I used had 1 row of MK4096-11, 1 row of MK4116-3 and an MOS MPS6502 date code 0578.

I have been using 16K DRAM’s on my Apple 1 since 1980 and have both a 20K and 32K mimeo that are the only ones I use and I have never had a problem with the DRAM’s (except they sometimes die).

In post #4, wsander wrote:

"but the 4K DRAM is no better than the 16K DRAM because the 8T97’s tri-state the RAM data a little before the end of CAS".

True, but this can be remedied easily by adding a small RC delay at the 8T97's enable inputs.

The worse situation is when the internal data bus of the DRAM subsystem starts floating too soon and the 8T97 see that and actively drive the CPU's data bus with the 'bit vapors' they see on their inputs. This is what happened with my own 20k Byte extension. There is not much capacitance on this internal bus except for the DRAMs and this depends on the parasitic capacitance on their output drivers. Adding these 39 pF capacitors brought remedy, it almost always works, but sometimes it doesn't. If I wanted to make a joke, I'd say it depends on the phase of the moon whether it works or not. (More likely, it depends on the humidity in my house and the amount of potentially conductive dust on the tablecloth that Apple-1 sits and is in contact with, this one has no rubber feet).

In general, it is considered bad engineering / bad design to have 'floating' signals and then hoping they would persist long enough, by parasitic capacitance, for the system to work. There once were industrial designs who intentionally used that 'dynamic logic' style trick on the PCB board level. The National Semiconductors IMP-16 microprocessor chip set comes to mind. Five to six PMOS ICs to make a Data General Nova compatible CPU. Early '70s, 1973 or so. It won't work without plenty of parasitic capacitances on certain signals. Whether this "feature" caused its early demise I don't know. Could be. One of the important virtues of 1960's minicomputers was that they did not need a tightly air conditioned room like the mainframe computers did. So these minis could be used in a lab environment or in industrial environments, where the air was dirtier and more humid. I don't think that the IMP-16 liked these harsher environments - despite it was designed into one of the early computerized engine diagnosis machines used in car garages / workshops. I would not put any of my money on a bet claiming it did work for long under these environmental conditions. But there are remedies, of course. Clean / degrease the PCB in a freon bath (a chemical now forbidden) and then conformally coat it with a plastic spray. That would help.

But still, running a microcomputer on 'bit vapors' is not a good idea. In case of the 6502, the slower ones don't see crumbling bits on the data bus for quite a while as their internal workings are pitifully slow. But the faster specimen of 6502 see these crumbling bits earlier than the slower ones made before the optical mask shrink.

It's a hit-and-miss. As we don't design MCAS system for Boeings, we can experiment and some of these modified Apple-1 will work, while others won't work reliably, because they are running on those 'bit vapors'. As long as experimenters are aware of the problem (and potential remedies, such as adding more parasitic capacitance) no harm is done except of some frustrating moments. This is why I wrote my warnings.

- Uncle Bernie

I understand that with the 16K DRAM the DRAM outputs can float until the next DRAM read cycle which can be a very long time and the voltage can reach near the “floating input level” of the 8T97. The Apple 1 does not turn on the 8T97s until the next DRAM read cycle starts so the 8T97s can have an uncertain output from the beginning of the cycle until after the CAS access time. I don’t see how that hurts anything other than maybe some noise as long as it satisfies the setup and hold time for the 6502. Pull-up resistors on the floating lines might be a better solution than Caps if you see a problem.

I myself have never seen a problem with 16K parts on an Apple 1. When I got my Apple 1 in 1976 I immediately replaced the 8 4K DRAMs with 32 Bipolar 4K DRAMs I had developed at Fairchild R&D labs and in about 1980 I replaced those with 16 16K MOS DRAMs with no problems. I currently use a Mimeo with 20K and a Mimeo with 32K with no problems, and they sometimes run for days or weeks. I have used 16K’s on Mimeos from the first one I got.

Maybe it's the weather in Cupertin0

I can walk to the Jobs house from where I live now.

Can't you design a PCB for this? It's really difficult to solder the leads onto the chip and components. Also where does the resistor lead go to inside of the chip?

Wendell Sander created a nice document how to do the 20K/32K mod:

https://apple1notes.com/wp-content/uploads/2020/07/Apple-1-32K-and-20K-Memory-Upgrade20130615.pdf

There is more to find: https://apple1notes.com

Yes, wsander is the same person.

Since many years there are much easier ways to expand the RAM, like it is done here: https://www.applefritter.com/content/apple1-iecmem-card-released or on the french RAM ROM card you have.

Maybe someone is willing to redesign the Apple 1 Mainboard to adopt an EPROM instead of the PROMs, an SRAM instead of the DRAMs, with the freed up space it would be easy to build in the 2519 replacement and another EPROM for the 2513.

If a good replacement for 2504 is found all parts would be 5V only that would simplify the powersupply also.

I am not sure but I think two 2114 and a 4040 binary counter can be an alternative.

I think its actually a bit easier to solder the diode and resistor on the underside of the board rather than the top to be honest.