I'm reasearching the Apple I tape interface. The function of the LS02, LS10, and LM311 is obvious. Are the 6301-IJ, 7623L chips ROM, or are they 6301 microcontrollers? I know the wonder book contains notes on the tape interface...somewhere, so I will begin the 230 page search.

Anytime now a bunch of really cool Apple I documets will get added to the archive.

http://coinop.org/kb_dl.aspx/kb/gametech/rom-ram_reference.html

the 6301-1 is a 256x4 memory. I don't suppose Apple ever released schematics or assembler listings for the casette card?

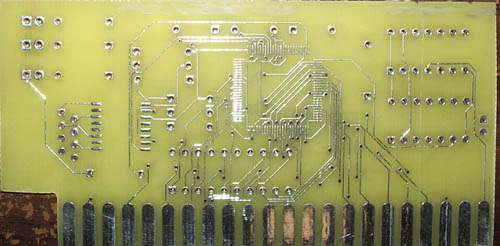

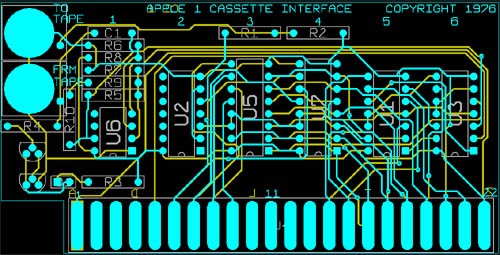

From the pictures I'm going to map what I can, and try to fill in the blanks based on what "should" be there.

It was easy to rule out a 6301 microcontroller, considering it has 40 pins.

Questions:

There is a schematic of a casette interface on page 64 of the

Wonderbook. The schematic appears to be preliminary to the Apple I.

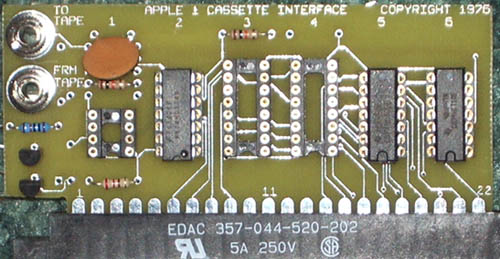

I need someone with an Apple I card to identify the 4 resistors under

the capacitor. I would also like an ID on the two transistors (they

are boxed in white). Any markings will help. Please also look at the

trace that wraps around the transistors from the red diode. Does it

connect to the collector of both transistors? (I'm assuming at least

the bottom is NPN due to the connections)

Anyone with any documentation on the casette interface would help.

The Wonderbook is not literally very clear in this area. I have all

the schematic drawn but the address decoding logic. I'm almost done

prooving it out and will post it sunday night. My goal is to have

gerber files ready sunday evening to get two of these casette boards

made. Verification of resistor values is not critical for this, but knowing the transistor situation is. A picture from a lower left angle of the board would help me.

NOTE: the traces seen over the chips are what is on the bottom of the board.

Any questions or comments? Its 3:30AM in Alaska. The east coast is waking up...

Thanks for the help.

Otherwise it will take dialup people forever to see it. Instead of image use thumb. Here is the schematic for the apple 1 cassette:

Hope this helps,

Vince

Yes, that helps. I wish I'd found that earlier! Amazingly my schematic matches that one exactly except for the component values. Its fairly easy to rule out which traces pass under the chips based on previous traces.

Amazingly my schematic matches that one exactly except for the component values. Its fairly easy to rule out which traces pass under the chips based on previous traces.

However, in the note section next to the chip select on pin 21 it says to jumper R to C. pin 21 on the interface is chip select T according to the apple manual. Did I miss something? I can't edit the post to change the picture size.

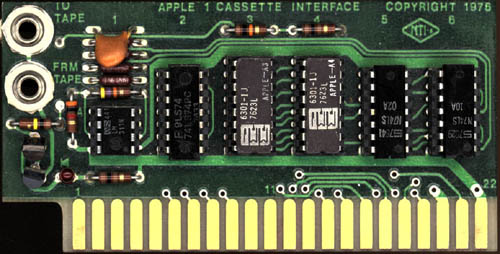

To a degree that is reasonable I'm making the card clone look exactly like the one pictured.

Yes, R (expansion pin 21) to C (74154 pin 14) jumper would be the address decoder for $C000. In order for the apple 1 to use the cassette interface the address decoder The apple 1 gave hard-wired memory decoding options. Always fun to try and reverse engineer a board but good job. If you look at the schematic of the apple 1 at IC B9 the 74154 /CSC is the C Woz is referring to. Looking closer at the 74154 you can see every output is for 4K blocks for the ability to actually address upto the full 64K of memory range. The 44pin card only had enough room for 3 memory selects so Woz left the choice up to the user but for the cassette, R needs to be jumpered to C so that the cassette interface code is at C100 (because A4 is selected on the card). Sorry, I'm going on, hope this helps too.

Vince

The 256 bytes of cassette interface ROM contain console input and evaluation of parameters (about 130 bytes, the code is very clear and some routines are similar to the monitor ROM, or same only using differet registers (X instead of Y or so), ECHO subroutine from monitor ROM is used) and tape I/O itself (cca 100 bytes) - code is not so clear here, with many nested loops and entry points to subroutines.

As soon as I will found it, I will post the tape interface source code here (if nobody will be faster than me).

Go ahead and post your findings. Knowing the locations in memory of the cassette hardware would help figuring out those loops. I bet they are for encoding and decoding the data. The Apple 1 cassette adaptor is similar to the Disk II and IWM, it requires very specific processor timing to read the data.

All right, I made my images much smaller this time.

I blured the top of this board. Tell me what it does. The surface mount chip on this boad has 4k of ram.

Here is the board I drew up last weekend. I placed the components within +-.050 of the origional board. The traces, an autorouter took care of that. I am not TOO crazy.

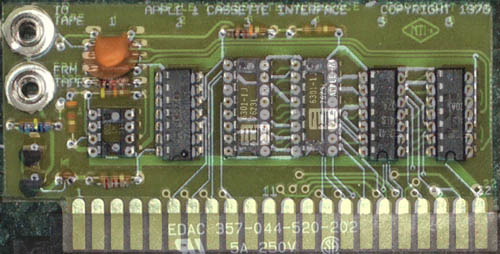

Here is the real one in case you forgot.

And the real one with mine on top of it. (to see how close the parts are) Even the labeling is "close". I didn't spend more than 10 seconds on this, so its not very well alligned.

I didn't spend more than 10 seconds on this, so its not very well alligned.

My last attempt to slow down the internet:

Have fun. I'll upload the gerber files once it's been tested. I don't want to be responsible for people wasing their money on an untested board.

First I would like to say HI! I'm new around here. I will soon be

building a Replica 1.

Has anyone produced a working cassette interface replica?

Welcome to the forum, rasterscan, and to the world of the Apple-I. Up to now, no one has announced that they have a working cassette interface for the Replica-I. It seemed easy for Woz in the 70's but the duplication of his efforts seems almost imposible. Here's hoping all those out there with the skills needed will have lots of luck with this projsct soon.

Larry

>> Go ahead and post your findings. Knowing the locations in memory of the cassette hardware would help figuring out those loops.

>> I bet they are for encoding and decoding the data.

You are right, of course.

Here is it (use non-proportional font):

Logjam,

Your Cassette board looks great, but I do want to draw your attention to one small detail that may cause a great deal of trouble on your board. The power distribution traces, are way too small. Notice on the original board how wide the Vcc and Gnd traces are. Also note how direct they are routed.

Auto routers can be made to work for the signal traces, but power traces usually need special attention. Please consider revising your design in this area.

Sincerely,

Rich

I don't want to steal belegost1's thunder, but since I had already written an insanely detailed annotation of the Apple-1 cassette ROM code while working on my emulation of the cassette interface for MESS, I figure that others should be allowed to benefit from it.

Sorry about how the above code came out; something seems to be wrong with how this board's software handles the "code" tag. And what's with the substitution of "l-e-g-o" with "EvilBlockCompany"?

This has to be the most complete (and best) commented disassembly of the cassette code for the Apple-I that I have ever seen. Great Job!